一、半导体Fab中的岗位介绍

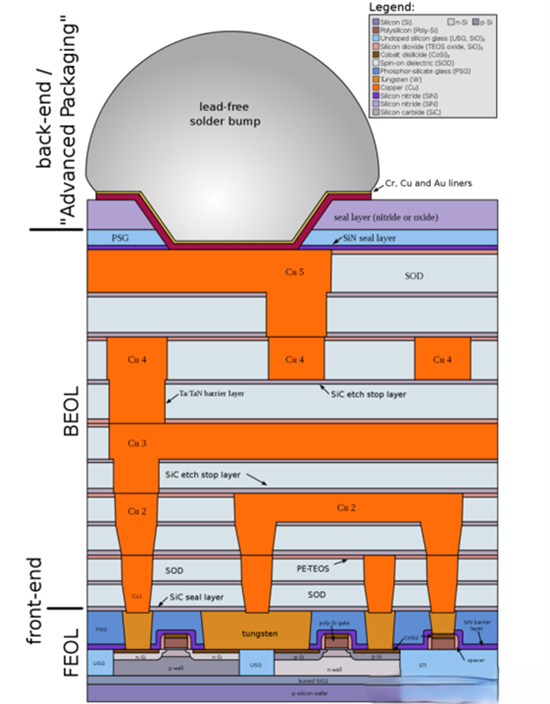

下图是一张集成电路内部结构示意简图:

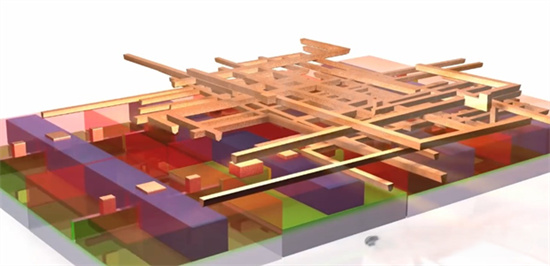

芯片结构的3D示意图如下所示:

从本质上来讲,芯片的内部物理结构就是一个具有多层图案结构的堆叠,并且层与层之间实现了有序互连。

从材料来讲,每层结构的组成无外乎为半导体材料、导体材料、绝缘体材料。

按照工艺段的顺序,大体上可以分为前段工艺(FEOL)和后段工艺(BEOL)。

简单地理解,FEOL部分主要负责形成CMOS晶体管结构,BEOL部分负责进行金属布线。

实现这些结构主要利用几大工艺模块轮番上阵、相互配合:光刻、刻蚀、薄膜沉积、CMP(化学机械抛磨)和Implant。

这些工序就涉及到和Fab中Module打交道了,module就是模组,指每种工艺对应的负责部门。

二、Fab中主要加工工序介绍

1.FUR(Furnace)——炉管

作为PIE,需求与FUR对接的工作主要有两点,一是氧化物的生长,二是退火。

加热一听就很费能量,这步很贵,因此厂内会严格控制ANNL站点数量,也造成了该部门的PE自由度很低(个人感觉也导致了含金量较低)。另外就是除非新建flow,否则任何FUR RCP的试用申请,都需会议通过。不像其他部门跟PE沟通即可。PIE只需要知道厂内有哪些FUR条件就可以,基本不会为单独产品新建条件。

所有炉管工艺都要进行污染管控,同时进入前必须有前清洗工艺,未清洗极容易造成沾污。一般poly裸露就是有污染风险,Oxide全覆盖就是没有。

(a)氧化物的生长——干法氧化(Dry Oxidation)。

一般就是走Si+O2=SiO2这个反应。

这种方式消耗wafer外延层(epitaxy层)中的Si,按照45:100的比例生成SiO2。生长速率随着SiO2厚度增加不断降低,因为O2更难与Si接触。干法氧化产生的Oxide质量最佳,内部缺陷最少,但是生长速率也是最慢的。工艺温度900-1200℃都有,低于700℃不成。

通常被应用于1000A以内Oxide的生长(说明:1A=10E-10m=0.1nm。A上面应该有个小圆圈○,才是正确标记,读作埃。)如Gate Oxidation,比较关键的工艺,决定Mosfet的Vth参数。

(b) 氧化物的生长——湿法氧化(Wet Oxidation)。

氢气氧气按比例通入腔体,生成水H2O。然后2H2O+Si=SiO2+2H2反应生成SiO2。可以看出来H2在这个过程中并不消耗,好在炉管一直有气体交换,不至于爆炸。氢:氧比例必须保持低于2比1,通常1.8:1。这个工艺生长SiO2较快,消耗比例也是0.45。因此可用于理论上0-20000A厚度的SiO2生长,当然实际应用中很少有厚于10000A的,暂未听说。

选择湿氧主要是为了保证质量的同时,节约成本。如果是大几千A的氧化物生长,干法实在是无能为力。而使用CVD等方式进行沉积,存在多种问题,如底部和拐角沉积不满,氧化物致密度低,电性差等问题。湿氧介于两者之间,还是靠谱的。

(c) 退火Anneal。

IMP在Si中注入离子(磷P,砷As /硼B,镓Ga等),会导致被注入层原子被撞击,而损伤晶格,而且注入离子也不在晶格上,处于间隙中。所以需要退火修复晶格缺陷,并将注入离子激活,进入晶格点。没有什么说法,一般也都是固定工艺,按照客户条件来即可。ANNL决定离子推进深度,即P区N区深度。

PS:该工艺与干法氧化有些相近,同样会产生5-20纳米左右的Oxide。纯净的Oxide,可以阻拦P元素的扩散,因此改变了wafer的污染等级,工程片跳过IMP站点时,必须注意。

(d)快速热退火(RTA)。

用极快的温度在短暂时间(如30s)内对wafer处理。因为时间极短,因此可以激活离子同时避免离子扩散。对于超浅结的制备很有价值,看情况使用,应用肯定会越来越广。

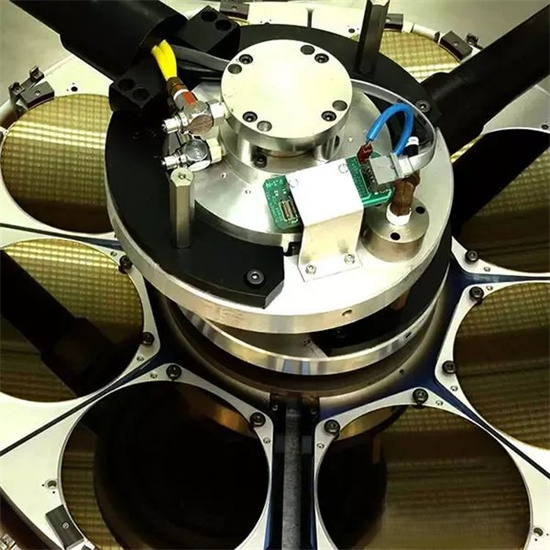

2.IMP (Implant)——离子注入

离子注入是通过高能机台构建大电磁场,然后将电离完成的离子射出(带电才能加速嘛),注入到wafer EPI层中的一种工艺。是个纯物理过程,注入的是离子。注入完会进行电中和,产出wafer不带电。

该工艺目的是,在wafer上注入特定浓度的特定离子,以完成对区域的掺杂,形成P区N区。然后构成PN结,NPN三极管之类的结构。

PIE与IMP对接的点似乎只有新建RCP,就像客户与IMP的沟通桥梁,按照仿真给出的IMP剂量,能量,角度,离子种类四个参数,去查询有无对应RCP。有就发个邮件申请使用,没有就申请新建。然后让IMP帮忙看看,机台能不能用(很多时候,IMP和FUR机台会管控过货,如果届时不能用很可能导致半夜被call,甚至加班)。这个部门我同样不清楚主要工作量,感觉难点应该在厂商方面。但是非常忙,每个产品条件都不一样,感觉一直在建RCP(也可能是人都跑了导致的)。PIE这边申请条件一般都得提前好几天,否则人家不给建,不是很容易交流的部门。

IMP包括剂量,能量,角度,离子种类四个参数。剂量,就是单位面积,想向wafer表面注入的离子数,决定了器件的掺杂浓度,自然影响阈值电压Vth;能量,离子在电场中加速获得能量,决定了注入的深度。改变这能量同时,沟道深度一般也要改变,对Vth也有影响;入射角度,经典角度如22°,避免在晶格间隙中一往无前,注入到离谱深度,所以有时不用0°作为入射角度。要学的知识还是很多的,但感觉仿真时都已经决定了。

此外,离子注入一般是普注,不想注入的地方需用光刻胶PR覆盖,或者用厚热氧阻拦。IMP是与WET有联动的部门,与PH也有一定关联。

3.WET(wet etch)——湿法蚀刻

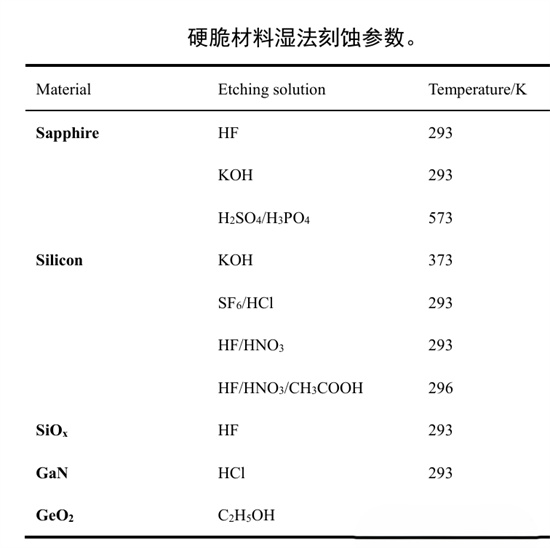

湿法是采用药液,进行各向同性蚀刻的一道工艺,总之就是wafer丢进水里,水能接触到的位置,都会被蚀刻。而干法刻蚀,就是wafer丢到太阳底下,光能照到的地方,会被蚀刻。

一般用于SiO2和Si的去除,也用于SiN,Si等材料。通常采用氢氟酸和氟化铵按照1比几十比例混合的药液,进行刻蚀。实际药液种类有几十种,能针对各种工艺,进公司后会有培训了解。在12寸厂,这些听起来吓人的液体基本接触不到,无须担心。但在8寸和6寸厂,仍有人工wafer蚀刻的工艺,需正面接触药液,进厂前需打听清楚,不一定能接受。

各向同性是WET的特点,因此很难使用光刻胶形成特定的图案,这是不如干法刻蚀的一点。而且还要避免药液渗入光刻胶底,造成掏空现象,这在离子注入步骤中可能会出现。但各向同性也有好处,对于侧壁生长的Oxide也可以完美去除。而干法刻蚀通常会刻蚀出一个有角度的斜面,侧壁深处的东西基本刻蚀不掉,需要其他手段。

PIE在确认PRS的时候,一般用现有条件先报废wafer并SEM测试。看形貌是否符合要求,然后提供蚀刻前后的形貌图给PE,他们可以一定程度计算出刻蚀速率(因为刻蚀过程形貌会改变,而且不同产品clear ratio也有差异,只能得到大概值)。之后根据速率提供RCP来优化PRS,直至满足要求。

一般WET用于功率器件的沟道形成,其深度是关键参数,可能与WET需要就这个工艺进行多次切片确认。不像FUR和IMP,基本上就是提申请,对方同意即可。

不同氧化物,如热氧,PETEOS,OZTEOS,HDP等等,都有不同的刻蚀速率,具体还要看膜层结构。

总体上感觉,这个部门技术含量高一些,虽然大部门ETCH站点都已被干法刻蚀取代,但湿法的存在还是很有必要性(而且清洗站点也全都是湿法)。

三、薄膜生长技术介绍

薄膜TF(thin film)底下有PVD,CVD和CMP三个小部门。

个人感觉技术含量都挺足,PVD和CVD在薄膜特性、种类,沟槽(Trench,TCH)填充等方面,都有很多的研究。

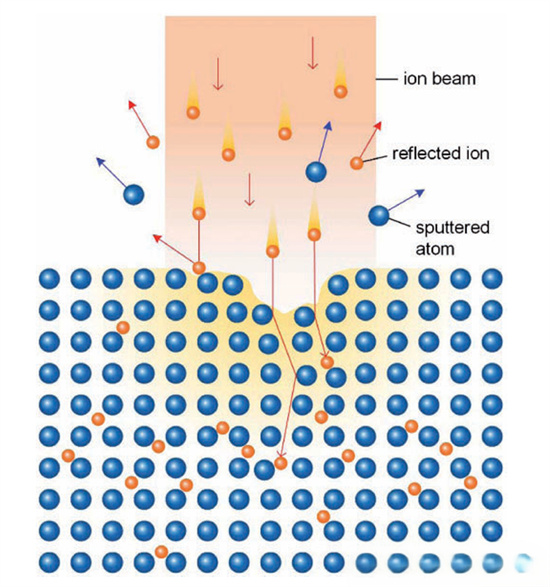

1.Physical Vapor Deposition——物理气相沉积PVD

物理气相沉积,顾名思义,整个薄膜沉积过程只有纯粹的物理反应,溅射出来的原子,一层一层的往wafer上堆叠,最终得到的是非晶材料(当然退火一下可以再结晶)。整个沉积过程,通常可以把wafer的温度保持在100℃以下,加上超高真空环境(<E-10mTorr量级),可以确保薄膜质量很高。

2.Chemical Vapor Deposition——化学气相沉积CVD

化学气相沉积,是通过在腔内通入混合气体,使其相互反应,在硅片表面沉积一层薄膜的工艺。通入的气体常温下非常稳定,沉积过程给wafer加热至较高温度,这样就可以确保反应在wafer上进行。

氧化物种类很多:

1. 最常见的SiO2,无人不知无人不晓(用O2/N2O等氧化SiH4的方式);

2. 沉积掺杂氧化物,如PSG/BPSG/FSG等,用于ILD和IMD膜层,过1000h可靠性考核很有用。目前功率芯片很多都是用于车规产品,要求1000h,175℃的可靠性测试(HTRB,HTGB,H3TRB等)。而一般的消费产品,只要求150℃,有的只500h可靠性测试通过即可。

3. 可以沉积隔离用氧化物O3TEOS(正硅酸乙酯)等,一种臭氧和四乙基硅烷的反应物。如果器件需要一定厚度的Oxide用来提高耐压,那就有两个选择,一是直接炉管热氧搞起来。但是如果Oxide太厚,就会选择部分热氧,部分TEOS叠加的方式,这在功率器件中很常见,甚至被用于栅氧的生长。而且TEOS的台阶覆盖性很好,不会出现拐角填充薄弱的情况。除了这些呢,还有比较关键的:

4. HARP的沉积,HARP是指高深宽比填充工艺,专门用于沟槽填充。其反应机理与TEOS差不多,所用气体也相近。但是可以填充的效果远超4:1,5:1这种程度,在90nm节点以下,会经常被采用。为了实现更高的填充比,有时也与蚀刻工艺循环进行,可以参考后文PECVD中,HDP工艺。5.Si3N4为主的氮化物的沉积,这种材料无论是强应力改善翘曲,还是杂质离子隔离,作绝缘材料,亦或是当CMP的阻挡层,都可以,介电常数还很高。还有我记不住的功能,总之用处多多。

以上,无论哪种功能,建flow时候都用得上。至于台阶覆盖性好,是因为气息必须先在wafer表面反应成核,然后才能延伸成为薄膜,较少在真空中直接反应。与PVD撒面粉一样的沉积方式,原理不同。

3. 化学机械研磨——Chemical Mechanical Planarization,CMP用途:可以将wafer的表面,整体进行平坦化。

除了这些呢,还有比较关键的:

4.HARP的沉积,HARP是指高深宽比填充工艺,专门用于沟槽填充。其反应机理与TEOS差不多,所用气体也相近。但是可以填充的效果远超4:1,5:1这种程度,在90nm节点以下,会经常被采用。为了实现更高的填充比,有时也与蚀刻工艺循环进行,可以参考后文PECVD中,HDP工艺。

5. Si3N4为主的氮化物的沉积,这种材料无论是强应力改善翘曲,还是杂质离子隔离,作绝缘材料,亦或是当CMP的阻挡层,都可以,介电常数还很高。还有我记不住的功能,总之用处多多。

以上,无论哪种功能,建flow时候都用得上。至于台阶覆盖性好,是因为气息必须先在wafer表面反应成核,然后才能延伸成为薄膜,较少在真空中直接反应。与PVD撒面粉一样的沉积方式,原理不同。

3. 化学机械研磨——Chemical Mechanical Planarization,CMP

用途:可以将wafer的表面,整体进行平坦化。

需要这个工艺的原因很明显,前面各种CVD,PVD工艺,还有ET,WET,FUR等等,大家伙沉积薄膜的时候都有些随性,有的注重侧壁,有的阴影效应明显,还会挖出沟槽。最终都会导致,wafer表面变得坑坑洼洼,同一层薄膜存在明显的高度差,因此需要CMP。

CMP过程:下方一个施加压力的抛光头,在wafer表面旋转,并不断位移。这个过程会不断添加磨料,wafer表面同时受物理/化学反应,最终被不断减薄直至特定厚度。

这个过程中,化学反应很关键,并非依靠压力生硬的摩擦,因此在特定薄膜层会出现研磨不动的情况,即无法反应。这样可以使CMP工艺在stop层停止,实现很好表面的平坦化。

当然,CMP过程中还有系统监控,实时量测并反馈wafer多个点的薄膜层厚度,进而调整研磨头在不同位置的压力,保证均一性。

因为有时候,flow中需要加一道CMP工艺,来确保形貌开发符合要求。就需要PIE和CMP PE一同,研发这道工艺。PIE需要选择APC系统量测的位置,厚度参数,并反馈给CMP,他们进去调整RCP,最终完成。

因为一般量测位置,都不在功率器件的核心处,因此需要PIE多次切片确认量测点,与实际厚度关系。并且选定窗口范围。毕竟CMP完成后只是比较平,但也会存在100nm至几微米的波动。CMP很贵,能不加就不加。安徽博芯微半导体科技有限公司,为核心组件提供高精度Showerhead服务,产品主要包括Shower head、Face plate、Blocker Plate、Top Plate、Shield、Liner、pumping ring、Edge Ring等半导体设备核心零部件,产品广泛应用于半导体、显示面板等领域,性能卓越,市场认可度高。

信息来源:知乎 作者:星火点灯有个梦